Vasudev Gohil

Thanks for visiting! Explore my site to learn more about me, my background, and what I have to offer. If you have questions or would like to discuss an opportunity to work together, feel free to get in touch.

About

Background

I am a Software Engineer at Siemens Industry Software Inc. I work at the intersection of machine learning and chip design. On my own time, I research the security of AI-based systems, especially LLMs. I hold a Ph.D. from the Department of Electrical and Computer Engineering at Texas A&M University, where I worked at the intersection of machine learning, hardware chip design, and security under the guidance of Dr. JV Rajendran. Before that, I did my undergraduate studies in the Department of Electrical Engineering at IIT Gandhinagar.

Research Interests

-

Machine Learning: Reinforcement Learning and Large Language Models

-

Security of AI

-

Red-Teaming LLMs

-

Adversarial Robustness

-

ML for Chip Design and Hardware Security

-

Embedded Systems Security

-

Security of Integrated Circuits Supply Chain

News

-

11/25: Excited to serve on the Technical Program Committee of ACM CCS 2026!

-

7/25: Excited to serve on the Technical Program Committee of USENIX Security 2026!

-

3/25: Excited to serve on the Technical Program Committee of NDSS 2026!

-

3/25: I released the findings of my independent research project "JBFuzz: Jailbreaking LLMs Efficiently and Effectively Using Fuzzing" on arXiv

-

3/25: Excited to serve on the Technical Program Committee of IEEE LAD 2025!

-

2/25: I presented our paper "LLMPirate: LLMs for Black-box Hardware IP Piracy" at Network and Distributed System Security (NDSS) Symposium, 2025

-

11/24: Our paper "LLMPirate: LLMs for Black-box Hardware IP Piracy" has been accepted at the Network and Distributed System Security (NDSS) Symposium, 2025

-

8/24: I presented our paper "AttackGNN: Red-Teaming GNNs in Hardware Security Using Reinforcement Learning" at the USENIX Security Symposium, 2024

-

8/24: I graduated with a Ph.D. degree from Texas A&M University. Excited to join Siemens and continue advancing the frontier of ML/AI for chip design!

-

6/24: Our paper "CreativEval: Evaluating Creativity of LLM-Based Hardware Code Generation" was presented at the LLM-Aided Design (LAD) Workshop, 2024

-

6/24: I successfully defended my doctoral dissertation on reinforcement learning for hardware security

-

5/24: Our paper "CreativEval: Evaluating Creativity of LLM-Based Hardware Code Generation" has been accepted at the LLM-Aided Design (LAD) Workshop, 2024

-

3/24: I presented our paper "MABFuzz: Multi-Armed Bandit Algorithms for Fuzzing Processors" at IEEE Design, Automation and Test in Europe Conference, 2024

-

2/24: Our paper "AttackGNN: Red-Teaming GNNs in Hardware Security Using Reinforcement Learning" has been accepted at the USENIX Security Symposium, 2024

-

1/24: IEEE Spectrum, IEEE's flagship publication, published a news article on our work on using Multi-Armed Bandit Algorithms for Fuzzing Processors, MABFuzz

-

12/23: I successfully defended my Ph.D. research proposal and have been admitted to Candidacy

-

12/23: Our paper "MABFuzz: Multi-Armed Bandit Algorithms for Fuzzing Processors" was picked up by Semiconductor Engineering (link)

-

11/23: Our paper "MABFuzz: Multi-Armed Bandit Algorithms for Fuzzing Processors" has been accepted at Design, Automation and Test in Europe Conference, 2024

-

11/23: Our paper "PSOFuzz: Fuzzing Processors with Particle Swarm Optimization" was presented at International Conference on Computer-Aided Design (ICCAD), 2023

-

10/23: My research abstract "Reinforcement Learning Frameworks for Protecting Integrated Circuits" has been accepted at SRC@ICCAD 2023. I also received a grant from ACM SIGDA to attend the SRC event and present a poster on my research.

-

8/23: Our paper "DETERRENT: Detecting Trojans Using Reinforcement Learning" has been accepted at IEEE Transcations on Computer-Aided Design of Integrated Circuits and Systems (TCAD)

-

7/23: Our paper "PSOFuzz: Fuzzing Processors with Particle Swarm Optimization" has been accepted at International Conference on Computer-Aided Design (ICCAD), 2023

-

7/23: Our paper "ExploreFault: Identifying Exploitable Fault Models in Block Ciphers with Reinforcement Learning" was presented at Design Automation Conference (DAC), 2023

-

2/23: Our paper "ExploreFault: Identifying Exploitable Fault Models in Block Ciphers with Reinforcement Learning" has been accepted at Design Automation Conference (DAC), 2023

-

11/22: The winners of the "AI vs. Humans" competition have been announced. Thank you to all the teams for participating!

-

11/22: Our paper "ATTRITION: Attacking Static Hardware Trojan Detection Techniques Using Reinforcement Learning" was presented at ACM SIGSAC Computers and Communications Security (CCS), 2022

-

10/22: Finalists for the "AI vs. Humans" competition have been announced (link)

-

09/22: "AI vs. Humans" competition is now live

-

09/22: Our paper "ATTRITION: Attacking Static Hardware Trojan Detection Techniques Using Reinforcement Learning" has been accepted for publication at ACM SIGSAC Computers and Communications Security (CCS), 2022

-

08/22: Co-organizing a first-of-its-kind competition, "AI vs. Humans" at Cyber Security Awareness Week (CSAW), 2022

-

07/22: Our paper "DETERRENT: Detecting Trojans Using Reinforcement Learning" was presented at Design Automation Conference (DAC), 2022

-

02/22: Our paper "DETERRENT: Detecting Trojans Using Reinforcement Learning" has been accepted at Design Automation Conference (DAC), 2022

-

10/21: Our paper "Game Dollars Splits: A Game Theoretic Analysis of Split Manufacturing" has been accepted for publication at IEEE Transactions on Information Forensics and Security (TIFS), 2021

Awards

-

Top Picks in Hardware and Embedded Security Nominee, 2025

-

Ph.D. Forum Nominee, DAC 2025

-

Ph.D. Dissertation Competition Nominee, HOST 2025

-

Ph.D. Forum Nominee, DATE 2024

-

ACM Student Research Competition Nominee, ICCAD 2023

-

ECEN Department Graduate Merit Fellowship, Texas A&M University, 2018

-

Academic Excellence Scholarship for securing top position at IIT Gandhinagar, 2014-2015

-

Dean's List at IIT Gandhinagar, 2014-2015

-

Travel Awards: ACM SIGDA Travel Grant to attend Student Research Competition at ICCAD, 2023; Design Automation Conference Young Fellows program, 2023; IEEE HOST Student Travel Grant, 2023; Texas A&M University ECEN Graduate Student Travel Grant, 2022; USENIX Security Travel Grant, 2021; IEEE HOST Student Travel Grant, 2020

Publications

-

V. Gohil, "JBFuzz: Jailbreaking LLMs Efficiently and Effectively Using Fuzzing," on arXiv, 2025

-

M. DeLorenzo, P. Tieu, C. Chen, V. Gohil, and J. Rajendran, "Watermarking LLMs—Challenges and Opportunities in Electronic Design Automation," in IEEE International Conference on Omni-layer Intelligent Systems (COINS), 2025

-

V. Gohil, M. DeLorenzo, V. Nallam, J. See, and J. Rajendran, "LLMPirate: LLMs for Black-Box Hardware IP Piracy," in Network and Distributed System Security (NDSS) Symposium, 2025

-

M. DeLorenzo, V. Gohil, and J. Rajendran, "CreativEval: Evaluating Creativity of LLM-Based Hardware Code Generation," in IEEE LLM-Aided Design (LAD) Workshop, 2024

-

R. Kande, V. Gohil, M. DeLorenzo, C. Chen, and J. Rajendran, "LLMs for Hardware Security: Boon or Bane?," in IEEE VLSI Test Symposium (VTS), 2024

-

V. Gohil, S. Patnaik, D. Kalathil, and J. Rajendran, "AttackGNN: Red-Teaming GNNs in Hardware Security Using Reinforcement Learning," in USENIX Security Symposium, 2024

-

V. Gohil*, R. Kande*, C. Chen, A. Sadeghi, and J. Rajendran, "MABFuzz: Multi-Armed Bandit Algorithms for Fuzzing Processors," in IEEE Design, Automation and Test in Europe Conference (DATE), 2024

-

V. Gohil, S. Patnaik, H. Guo, D. Kalathil, and J. Rajendran, "DETERRENT: Detecting Trojans Using Reinforcement Learning," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024

-

C. Chen*, V. Gohil*, R. Kande, A. Sadeghi, and J. Rajendran, "PSOFuzz: Fuzzing Processors with Particle Swarm Optimization," in IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2023

-

H. Guo, S. Saha, V. Gohil, S. Patnaik, D. Mukhopadhyay, and J. Rajendran, "ExploreFault: Identifying Exploitable Fault Models in Block Ciphers with Reinforcement Learning," in ACM/IEEE Design Automation Conference (DAC), 2023

-

S. Patnaik, V. Gohil, H. Guo, and J. Rajendran, "Reinforcement Learning for Hardware Security: Opportunities, Developments, and Challenges," in 19th International SoC Conference (ISOCC), South Korea, 2022 (Invited)

-

V. Gohil, H. Guo, S. Patnaik, and J. Rajendran, "ATTRITION: Attacking Static Hardware Trojan Detection Techniques Using Reinforcement Learning," in ACM SIGSAC Conference on Computer and Communications Security (CCS), 2022

-

V. Gohil, S. Patnaik, H. Guo, D. Kalathil, and J. Rajendran, "DETERRENT: Detecting Trojans using Reinforcement Learning," in ACM/IEEE Design Automation Conference (DAC), 2022

-

V. Gohil, M. Tressler, K. Sipple, S. Patnaik, and J. Rajendran, "Games, Dollars, Splits: A Game-Theoretic Analysis of Split Manufacturing,” in IEEE Transactions on Information Forensics and Security (TIFS), 2021

-

C. Jin, V. Gohil, R. Karri, and J. Rajendran, “Security of Cloud FPGAs: A Survey,” in arXiv, 2020

* Equal Contributions

Select Projects Showcase

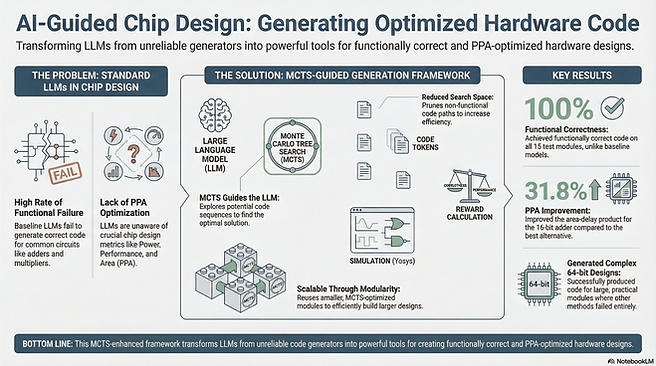

Note: The posters shown below are generated using an AI tool, so they may contain mistakes. Consider checking the complete paper for important information.

Experience

Software Engineer

Siemens Industry Software Inc.

September 2024 - Present

I work on the R&D team for Siemens EDA's Catapult business unit. My work focuses on developing ML/AI solutions for advancing the chip design process.

Graduate Research Assistant

ECEN Department

Texas A&M University

August 2018 - August 2024

I worked as a research assistant at the intersections of machine learning, specifically RL and LLMs, chip design, and hardware security. My work was primarily focused on applying machine learning to improve the chip design process and increase the security of the IC supply chain by designing solutions to thwart reverse engineering, intellectual property piracy, and hardware Trojan insertion.

Technical Intern

Silicon Realization Group

Synopsys

May 2022 - August 2022

I worked as a technical intern in the DSO.ai team in the Silicon Realization Group of Synopsys. I worked on the DSO.ai tool, the EDA industry's first autonomous artificial intelligence application for chip design. I assisted team members in their tasks and performed experiments to improve DSO.ai.

Research Intern

ECEN Department

Texas A&M University

May 2017 - July 2017

I contributed to an ongoing project in Dr. Shakkottai's research group. I helped modify and develop appropriate decision trees for QoS to QoE mapping with the help of machine learning methods.

Summer Research Intern

IIT Gandhinagar

May 2016 - July 2016

I contributed to an ongoing project in Dr. Chakraborty's research group. Initially, I performed a thorough literature review, and eventually, I worked with a Fiber Bragg grating as a pressure sensor.

Education

Ph.D. in Computer Engineering

Texas A&M University, College Station

August 2018 - August 2024

B. Tech in Electrical Engineering

IIT Gandhinagar

July 2014 - August 2018

Mentorship

- Matthew DeLorenzo - Ph.D. Researcher at TAMU

- Veera Vishwa Achuta Sai Venkat Nallam - Undergraduate Researcher at TAMU

- Joey See - Undergraduate Researcher at TAMU

- First position after graduation: HP

- Mark Tressler - Undergraduate Researcher at TAMU

- First position after graduation: AMD

- Kevin Sipple - Undergraduate Researcher at TAMU

- First position after graduation: MS at TAMU

Service

-

Journals: TIFS, TCAD, TVLSI, TCOMP, Access, ESL, TRETS, JETC, TODAES

- Conferences: CCS, USENIX Security, NDSS, ACSAC, LAD, DAC, DATE, ICCAD, ASP-DAC, HOST, ISVLSI, ICCD, VTS, ASHES

Let’s Connect

Email: vgohil.research@gmail.com

LinkedIn: vasudevgohil